Dans la recherche, on sait souvent d’où on part et où on veut aller. On imagine rarement les effets de nos travaux dans l’avenir. Il y a quelque mois, j’ai appris par hasard que mon travail de jeune chercheur avait contribué à transmettre sur terre les images de Titan, le plus grand des satellites de Saturne, obtenues le 14 janvier 2005, pendant la descente et l’atterrissage du module Huygens, de la mission Cassini. Une magnifique video créée pour le 10ème anniversaire de cette descente, nous raconte ce spectaculaire évènement.

Quelle relation peut bien exister entre ce jeune chercheur en électronique que j’étais et l’épopée spatiale? L’occasion de conter une belle histoire de science et de technologie, qui relie le début des réseaux numériques, le Minitel, la conception de circuits intégrés, le développement des premières technologies de compression d’image (JPEG et MPEG) aujourd’hui omniprésentes, et se prolonge du côté de Saturne… à plus d’un millard de km de la terre. L’occasion aussi de rappeler que la recherche est une magnifique aventure humaine, faite de fulgurances et de sueur, de hasard et de nécessité. L’occasion enfin de redire que la science nous apporte à la fois par sa simple pratique, qui nous perment de développe les connaissances sur lesquelles nous appuyer, et par ses applications, celles qui étaient recherchées au départ… comme celles qui n’étaient même pas envisagées. Et que le temps entre la recherche et ses applications peut aller de quelques mois… à plus de 20 ans, le temps qui sépare le début de cette histoire, en 1985, de l’atterrissage de Huygens en 2005.

1980 – Les premiers réseaux numérique et le Minitel

Revenons au début des années 80. Côté réseau, l’internet n’existe pas encore et les technologies qui fondent internet sont en développement. TCP/IP sera finalisé et le mot Internet sera adopté en 1983. Du côté du monde telecom, on envisage d’amener des services numériques aux entreprises via la norme RNIS, dont le développement lancé en 1980 sera finalisée en 1988.

En France, le ministère des PTT a lancé en France en 1980 le Minitel, le 1er accès grand public à des services numérique et envisager déployer le RNIS pour offrir aux entreprises les 1er services de visoconférence.

Vers 1985, les chercheurs, aussi bien des centres de recherche du ministère des PTT que chez les industriels, ont alors identifié deux sujets de R&D :

- les futures services numérique (évolution du Minitel, ou visiophonie d’entreprise) devront pouvoir bénéficier de compresion d’images fixe ou animées efficaces,

- pour être démocratisés, il sera nécessaire de baisser les coûts et d’implémenter dans des circuits intégrés spécialisés ces algorithmes de compressions très gourmands en puissance de calcul.

1985 – Les débuts de la compression d’image

C’est alors le début d’une extraordinaire course mondiale pour la maîtrise de ces technologies. La course commence du côté de l’image fixe. Entre 1985 et 1988, la commission européenne soutien le projet ESPRIT « PICA » (Photographic Image Coding Algorithm) avec une forte contribution des équipes françaises du CCETT à Rennes. Le consortium PICA crée et teste un 1er algorithme de compression numérique d’images basé sur une transformée mathématique nommée la Transformée en Cosinus Discrète (DCT). L’idée initiale d’utiliser la DCT pour la compresion d’images avait déjà 10 ans ![1]Ahmed, Nasir; Natarajan, T.; Rao, K. R. (January 1974), « Discrete Cosine Transform » (PDF), IEEE Transactions on Computers, C-23 (1): 90–93, doi:10.1109/T-C.1974.223784

En 1986 se met en place le groupe international de normalisation JPEG (Joint Picture Expert Group). Comme c’est souvent le cas, ce groupe compare de nombreuses propositions techniques, pour déterminer la technologie la plus prometteuse. En 1988, c’est la techologie proposée par PICA qui est sélectionnée, technologie qui formera la base de JPEG qui sera finalisé en 1992.

Pour les images video, la première version de la norme de visioconférence H.261, a été ratifiée fin 1988. Et le désormais célèbre comité MPEG a commencé ses travaux en 1988, avec une poignée d’experts sous l’impulsion de Leonardo Chariglione, du CSELT, qui sera un acteur décisif du succès de MPEG[2]Leonardo Chariglione’s Blog, The true history of MPEG’s first steps. Les travaux techniques sont en particuliers alimentés par le projet européen COMIS dont la commission européenne me demande d’être l’un des « reviewers ». J’ai alors la chance d’assister aux premières démonstrations de compression/décompression d’une video de Venise, spécialement choisie par le projet parce que les images ne bougaient pas trop. Le groupe MPEG publiera finalement la première norme MPEG1 en 1993.

Les équipes de recherche françaises au cœur du match

Au milieu des années 80, fraichement diplômé, j’avais rejoint Télécom Paris comme enseignant-chercheur. Mon équipe de recherche, dirigée par le professeur Francis Jutand, travaille alros sur la conception de circuits intégrés très optimisés et spécialisés pour le traitement du signal. A la même période, d’autres chercheurs français du CNET/CCETT, mais aussi de Thomson LER (Laboratoire Electronique de Rennes), Philips LEP (Laboratoire d’Electronique de Philips) sont très actifs sur la normalisation H.261 et MPEG.

Grâce à cet écosystème français, mon équipe de recherche prend conscience de l’importance de la dynamique mondiale sur la compression d’image. Nous nous mettons donc à travailler dès 1985 sur une architecture de circuit parfaitement optimisée pour la DCT, qui était alors le cœur des algorithmes de compression envisagées pour les photos et les video.

La puissance de calcul requise pour encoder ou décoder des images vidéo est très exigeante et le matériel requis pour le faire avec des processeurs à usage général extrêmement volumineux. Rappellons qu’en 1988, le microprocesseur le plus puissant est l’Intel386. Pour 299$, avec ses 275 000 transistors et sa vitesse d’horloge de 12MHz pour l’entrée de gamme, l’i386 a une puissance de calcul d’environ 5 Millions d’Instructions par seconde. La DCT demande environ 40 opérations par pixel d’image traitée. Le calcul d’une DCT pour une image de taille modeste (le format maximum d’image envisagé par H.261 pour la visiophonie est alors de 15 images par seconde, chaque image étant de 352 × 288 pixels) demande plus de 60 millions d’opérations. Bref, pour simplement comprimer un maigre flux video, il faut alors employer pas moins d’une douzaine de microprocesseurs i386, soit 3500$ d’équipement!

Pour essayer de faire baisser ces coûts prohibitifs et permettre de futures applications grand public, l’équipe de Télécom Paris, associé à celle du CNET de ParisA, invente une implémentation très efficace et, dès 1986, publie les premiers articles scientifiques sur le sujet[3]F. Jutand, N. Demassieux, G. Concordel, J. Guichard and E. Cassimatis, « A single chip video rate 16×16 discrete cosine transform, » ICASSP ’86. IEEE International Conference on Acoustics, … ...Lire la suite[4]N. Demassieux, G. Concordel, J. Durandeau and F. Jutand, « An optimized VLSI architecture for a multiformat discrete cosine transform, » ICASSP ’87. IEEE International Conference on … ...Lire la suite. En parallèle elle dépose deux brevets[5]Circuit pour effectuer une transformation linéaire sur un signal numérique EP 0241352 A1[6]Additionneur binaire comportant un opérande fixé, et multiplieur binaire parallèle-série comprenant un tel additionneur EP 0262032 B1.

L’idée-clé pour économiser de l’espace sur le silicium est que, dans une DCT, toutes les multiplications se font par une constante connue. Un multiplicateur par une constante nécessite beaucoup moins de matériel qu’un multiplicateur à usage général. Nous envisageons donc de crééer 88 multiplicateurs série-parallèle spécialisés pour une constante donnée, tous totalement différents les uns des autres, tâche qu’il est manifestement impossible de faire manuellement, mais que nous enviageons alors de faire en les générant automatiquement grâce à un logiciel.

STV3200 – 1er circuit au monde pour la compression d’image

Mais il faut faire vite : la rumeur circule dans le microcosme que les japonais vont être les premiers sur le créneau. L’équipe de Telecom Paris décide alors de sortir du seul cadre académique, et de se lancer dans la conception d’un vrai circuit industriel. A l’automne 1986, avec Francis Jutand, nous descendons à Grenoble et entamons des négociations avec SGS-Thomson (aujourd’hui STMicroelectronics).

A cette époque, l’équipe de conception interne de SGS-Thomson étudiait une solution en 12 puces, utilisant des FPGA. Il faut alors convaincre les responsables de l’équipe que notre solution était crédible. Un contrat de collaboration est signé fin 1986 entre Telecom Paris et SGS-Thomson pour licencier la propriété intellectuelle de deux brevets à SGS-Thomson, et mettre en place une équipe de conception conjointe qui concevrait la puce DCT courant 1987. L’équipe SGS-Thomson de Grenoble doit être saluée pour cette aventure, pour avoir fait preuve d’ouverture d’esprit en acceptant de modifier sa façon habituelle de travailler et pour avoir accepté l’idée innovante d’une équipe de conception mixte université/industrie. Il s’agit d’un cas unique (à notre connaissance) d’une puce industrielle développée par une équipe mixte académique/industrie. Cette collaboration va pourtant pour livrer la première puce de DCT au monde.

Alain Artieri, alors employé par SGS-Thomson vient s’intégrer à l’équipe de l’ENST, et nous développons ensemble, dans les locaux de la rue Barrault, le layout de la puce, dans la technologie CMOS 2 µm de SGS-Thomson. Toutes les vérifications (Design Rule Checking, simulation logique….) sont ensuite réalisées par SGS-Thomson à Grenoble.

Nous utilisons même des outils de CAO « maison », outils développés dans le langage de programmation LISP par nos collègues Michel Dana et Jean-Claude Dufourd développés . Le premier de ces outils, nommé « PREFORME » permettait de compacter localement le dessin d’un circuit esquissé manuellement[7]Jean-Claude Dufourd, Jean-François Naviner, Francis Jutand: Preform: A Process Independent Symbolic Layout System. ICCAD 1990: 248-251.

Le second outil est un « assembleur de silicium », que nous créons, une approche indispensable au vu de la complexité de nos 88 multiplicateurs. Il permet de générer par logiciel — et non manuellement comme cela se faisait à l’époque — la disposition physique de la puce dans son ensemble, par une approche connue sous le nom de « compilation de silicium » qui n’avait jamais été utilisée auparavant pour un produit industriel. Tous les routages complexes nécessaires pour connecter les multiplicateurs d’un algorithme DCT rapide ont également été programmés, ce qui a permis de gagner du temps et d’éviter les erreurs qu’un routage manuel aurait créées.

La conception de la puce a eu lieu entre janvier et août 1987. Après les traditionnelles nuits blanches pour valider le « tape out » (dernière version de la conception de la puce), le circuit est mis en production et les premiers échantillons, fabriqués en octobre 1987 sont testés avant la fin de l’année 1987. Ces premiers prototypes souffrent de quelques erreurs d’origine électriques, erreur provenant de la décision de notre partenaire industriel de ne pas mener certaines vérifications (Electrical Rule Checking). Les erreurs corrigées, une seconde fabrication a lieu en 1988.

Résultant de cette conception conjointe[8]Artieri A., Kirtter S., Jutand F. Demassieux N., A one chip VLSI for real time two-dimensional discrete cosine transform, International Symposium on Circuits and Systems 1988, la puce DCT STV3200 capable de traiter des blocs de taille variable allant de 4×4 à 16×16 pixel sera commercialisée en 1988.

Les normes JPEG et MPEG s’étant finalement fixée à 8×8 pour la taille des blocs, SGS-Thomson crée ensuite en 1992 une deuxième version de la puce (STV3208) optimisée pour les standards définitifs. La collaboration ENST / SGS-Thomson s’est poursuivie dans les années 1988-1990, menant à la conception de la puce d’estimation de mouvement STi3220 qui a été commercialisée en 1994.

Ces circuits intégrés STV3200 et STi3220 ont été les premières produits de ce qui est devenu plus tard la business unit SGS-Thomson Multimedia.

Par la suite, je regroupais les aspects théoriques de tout cet effort dans ma thèse, qui sera soutenue le 8 mars 1991 [9]Nicolas Demassieux, Architectures VLSI pour le traitement d’images : une contribution à l’étude du traitement de l’information, thèse de doctorat en électronique ».

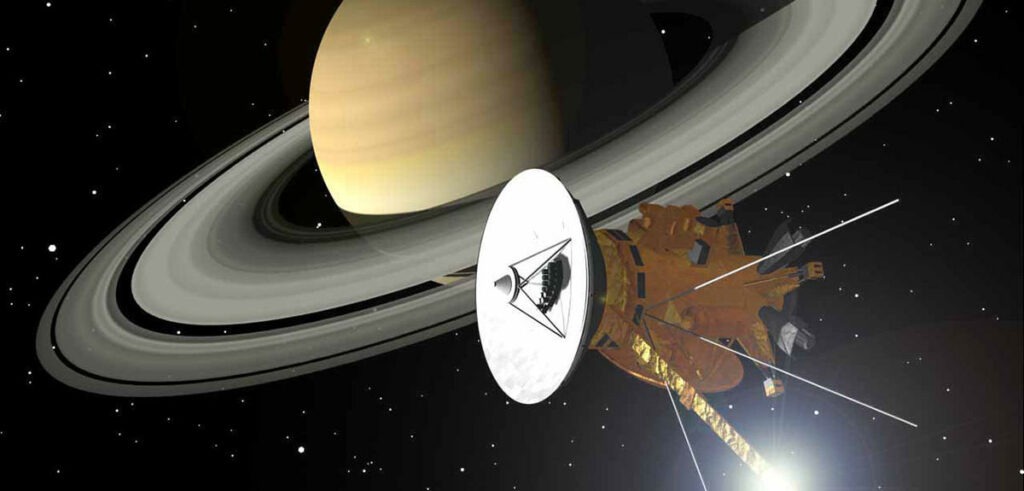

La mission Cassini-Huygens

25 ans après cette aventure, au détour d’une recherche internet, je découvre avec un grand étonnement que le circuit STV3200 a été utilisé pour la mission Cassini-Huygens.

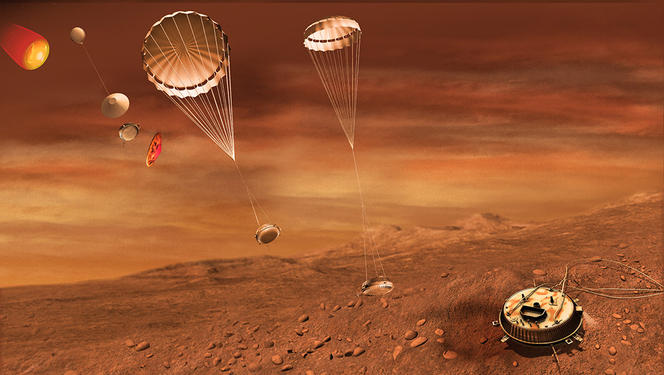

La mission est décidée par la NASA et l’ESA fin 1988-1989 : la NASA est en charge de la sonde Cassini elle-même, et l’ESA est en charge du développement de l’atterrisseur Huygens, qui doit se poser sur Titan, le plus gros satellite de Saturne, un astre mystérieux à l’athmosphère de méthane. Le développement technique s’étale entre 1989 et 1997, date du lancement. Huygens emporte divers instruments scientifiques, parmi lesquels un imageur nommé Descent Imager/Spectral Radiometer ou DISR[10]DISR, Plank Institute for Solar System Research[11]The descent imager/spectral radiometer, Space Science Review, 104: 469-551, 2002 – view . Le DISR dispose d’un unique capteur CCD de 520×256 pixels, alimenté par un faisceau de fibre optiques provenant de 4 systèmes optiques différents : un High Resolution Imager (HRI) de 160×254 pixels, un Medium Resolution Imager (MRI) de 160×254 pixels, un Side Looking Imager (SRI) de 175×254 pixels et Solar Aureole avec 4 zones de 6×50 pixels.

Le plan de la mission Huyens est de prendre environ 700 images régulièrement pendant les 2h30 de descente, et au sol, aussi longtemps que possible. Hugens et par ailleurs mis en rotation lente, Il faut imaginer, à cette distance du soleil, et sur le sol d’un astre très sombre, il fait plus que nuit noire (la lumière du soleil, sur Titan, n’est que 1% de celle que la terre reçoit). Il est donc prévu d’allumer un projecteur de 20W pour éclairer l’environnement dès que Huygens atteint l’altitude de 700m. Ces images, ainsi que les données collectée par les autres instruments scientfiques, sont transmises vers l’orbiteur Cassini par deux modules radio, chacun fontionnant à 8,2kb/s[12]The Hygens Probe System Design, Space Science Reviews 104: 155–189, 2002 – download. L’orbiteur retransmet alors les données vers la terre. Lorsque Cassini disparaît de l’horizon de l’atterisseur, la transmission s’arrête définitivement.

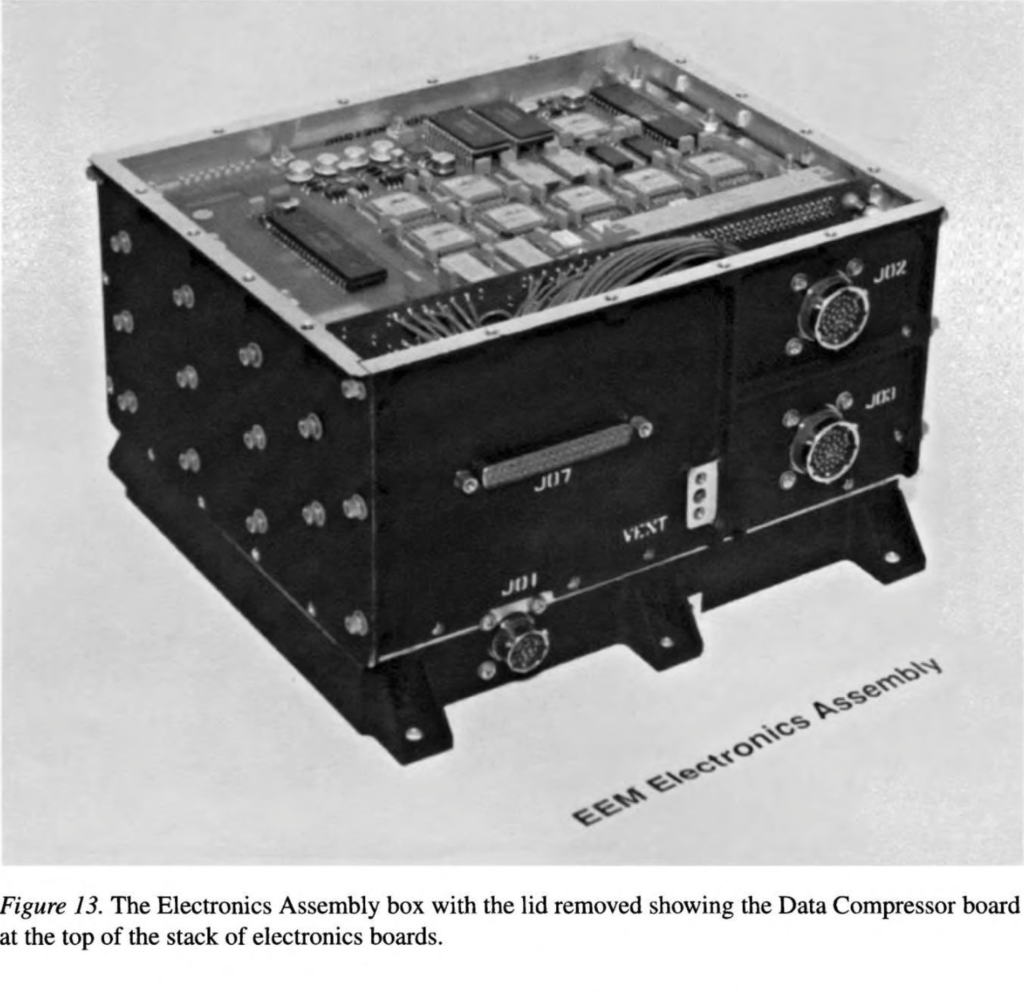

Chaque image pesant environ 500kb, la transmission d’une image non comprimée aurait demandé plus de 30s, ce qui n’était pas assez rapide pour collecter les données souhaitées. Il a donc été décidé d’ajouter un coprocesseur hardware, capable de comprimer les images à la volée. La conception de ce coprocesseur a été confiée à la Technical Universitat Braunschweig, qui décide d’y intégrer … le STV3200, un microprocesseur 80C86 et 8 FPGA Actel[13]The descent imager/spectral radiometer, Space Science Review, 104: 469-551, 2002 – view ).

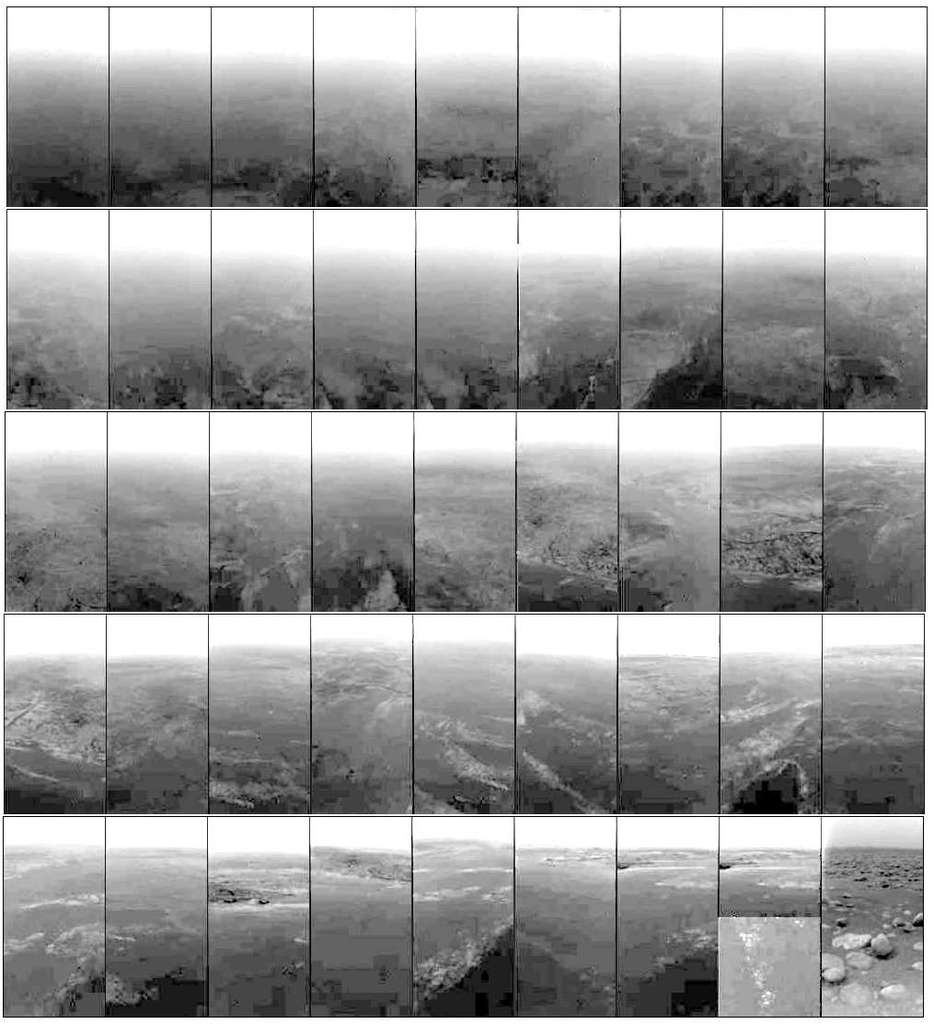

Le 14 janvier 2005 commence la decente de Huygens sur Titan. Pendant les 2h27 de cette descente, et 1h10mn sur le sol, un grand nombre d’images et de données brutes sont collectées. Cette video montre bien en accéléré toutes les phases de cette descente, mettant en scène le ballet bien orchestré entre les différents instruments.

Les 700 images prévues avaient été séparées en 2 lots, chacun, dans un soucis de redondance, devant être tranmis par l’un des 2 canaux radio. Ce choix de conception s’avère clé : l’un des deux canaux radio ne s’ouvre pas en raison d’une erreur de programmation et seules 350 images peuvent être transmises vers la terre.

Les 350 images brutes sont ensuite mises à disposition de la communauté; elles sont toujours en ligne[14]Raw images from the Huygens probe descent on 14 January 2005, ESA.

Scientifiques et amateurs eclairés s’en emparent. Elle sont à la fois la source de « belles images », soit colorées après utilisation des données de spectrométrie, soit assemblées pour former des images composites. Elles sont alors reprises par de nombreux médias. Les images sont aussi une source d’informations scientifiques importantes pour comprendre Titan[15]Cassini Final Mission Report, Huygens, 2019.

Epilogue

Les motivation initiales pour cette puce de DCT n’ont pas vraiment donné suite. Le minitel photographique ne sera jamais commercialisé. La visiophonie ne connaîtra jamais de réel développement dans sa version RNIS/H.261. Il n’y pas eu de marché, à l’époque, pour ces premières puces. L’histoire montrera qu’au moins une d’entre elles n’avait jamais été envisagée….

Mais cette implémentation hardware a permis à de nombreuses équipes de recherche dans le monde d’implémenter des codecs vidéo en temps réel, et a donc contribué à accélérer les recherches sur JPEG et MPEG, qui ont depuis connu un succès phénoménal, et des applications.

Je n’avais gardé que peu de documents sur ce projet. Aussi, ayant appri qu’un STV3200 s’était posé sur Titan, j’ai décidé de m’en procurer un sur eBay, comme un petit souvenir de tout à ça. Il est là, sur mon bureau, posé sur une image…. Je pense à son petit frère qui est depuis 15 ans dans le noir, par -180°C.

Remerciements

Je profite de ce petit retour arrière pour remercier les personnes qui ont, à un titre ou un autre, participé à cette aventure. Cette liste étant établie de mémoire, j’ai pu omettre quelques noms…

Alain Artieri, Joe Borel, Eric Cassimatis, Oswald Colavin, Gilles Concordel, Jean-Claude Dufourd, Jean-Pierre Durandeau, Michel Dana, Jacques Guichard, S. Kritter, Francis Jutand, Yves Mathieu, PY Le Panerer.

References

| ↑1 | Ahmed, Nasir; Natarajan, T.; Rao, K. R. (January 1974), « Discrete Cosine Transform » (PDF), IEEE Transactions on Computers, C-23 (1): 90–93, doi:10.1109/T-C.1974.223784 |

|---|---|

| ↑2 | Leonardo Chariglione’s Blog, The true history of MPEG’s first steps |

| ↑3 | F. Jutand, N. Demassieux, G. Concordel, J. Guichard and E. Cassimatis, « A single chip video rate 16×16 discrete cosine transform, » ICASSP ’86. IEEE International Conference on Acoustics, Speech, and Signal Processing, 1986, pp. 805-808, doi: 10.1109/ICASSP.1986.1169147 |

| ↑4 | N. Demassieux, G. Concordel, J. Durandeau and F. Jutand, « An optimized VLSI architecture for a multiformat discrete cosine transform, » ICASSP ’87. IEEE International Conference on Acoustics, Speech, and Signal Processing, 1987, pp. 547-550, doi: 10.1109/ICASSP.1987.1169851 |

| ↑5 | Circuit pour effectuer une transformation linéaire sur un signal numérique EP 0241352 A1 |

| ↑6 | Additionneur binaire comportant un opérande fixé, et multiplieur binaire parallèle-série comprenant un tel additionneur EP 0262032 B1 |

| ↑7 | Jean-Claude Dufourd, Jean-François Naviner, Francis Jutand: Preform: A Process Independent Symbolic Layout System. ICCAD 1990: 248-251 |

| ↑8 | Artieri A., Kirtter S., Jutand F. Demassieux N., A one chip VLSI for real time two-dimensional discrete cosine transform, International Symposium on Circuits and Systems 1988 |

| ↑9 | Nicolas Demassieux, Architectures VLSI pour le traitement d’images : une contribution à l’étude du traitement de l’information, thèse de doctorat en électronique » |

| ↑10 | DISR, Plank Institute for Solar System Research |

| ↑11 | The descent imager/spectral radiometer, Space Science Review, 104: 469-551, 2002 – view |

| ↑12 | The Hygens Probe System Design, Space Science Reviews 104: 155–189, 2002 – download |

| ↑13 | The descent imager/spectral radiometer, Space Science Review, 104: 469-551, 2002 – view |

| ↑14 | Raw images from the Huygens probe descent on 14 January 2005, ESA |

| ↑15 | Cassini Final Mission Report, Huygens, 2019 |

Retour de ping : Bretagne Ultra Trail 2022 – 59 km / 1200mD+ - Nicopedies